# PART TWO DIGITAL ELECTRONICS

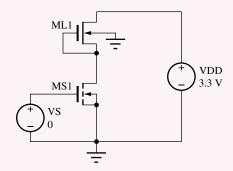

CHAPTER 6

INTRODUCTION TO DIGITAL ELECTRONICS 359

CHAPTER 7

COMPLEMENTARY MOS (CMOS) LOGIC DESIGN 462

CHAPTER 8

MOS MEMORY AND STORAGE CIRCUITS 515

CHAPTER 9

BIPOLAR LOGIC DESIGN 563

## **CHAPTER 6**

### INTRODUCTION TO DIGITAL ELECTRONICS

### **CHAPTER OUTLINE**

- 6.1 Ideal Logic Gates

- 6.2 Logic Level Definitions and Noise Margins

- 6.3 Dynamic Response of Logic Gates

- 6.4 Review of Boolean Algebra

- 6.5 Diode Logic and DTL

- 6.6 NMOS Logic Design

- 6.7 Static Design of the NMOS Saturated Load Inverter

- 6.8 NMOS Inverter with a Linear Load Device

- 6.9 NMOS Inverter with a Depletion-Mode Load

- 6.10 NMOS Inverter Summary and Comparison

- 6.11 NMOS NAND and NOR Gates

- 6.12 Complex NMOS Logic Design

- 6.13 Power Dissipation

- 6.14 Dynamic Behavior of MOS Logic Gates

- 6.15 A Final Comparison of Load Devices

- 6.16 PMOS Logic

Summary

**Key Terms**

References

Additional Reading

Problems

### CHAPTER GOALS

- Introduce binary digital logic concepts

- Explore the voltage transfer characteristics of ideal and nonideal inverters

- Define logic levels and logic states at the input and output of logic gates

- Present goals for logic gate design

- Understand the need for noise rejection and the concept of noise margin

- Introduce measures of dynamic performance of logic gates including rise time, fall time, propagation delay, and power-delay product

- Review Boolean algebra and the NOT, OR, AND, NOR, and NAND functions

- Explore simple transistor implementations of the inverter

- Introduce diode logic and diode-transistor logic circuits

- Explore the design of MOS logic gates employing single transistor types — either NMOS or PMOS transistors (known as single-channel technology)

- Learn basic inverter design; discover why transistors are used in place of resistors

- Understand design and performance differences between saturated load, linear load, and depletion-mode load circuits

- Present examples of noise margin calculations

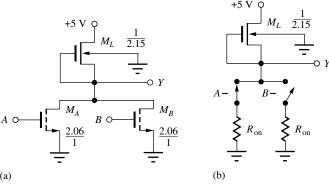

- Learn to design multiinput NAND and NOR gates

- Learn to design complex logic gates including sum-of-products representations

- Develop expressions and approximation techniques for calculating rise time, fall time, and propagation delay of the various single-channel logic families

Digital electronics has had a profound effect on our lives through the pervasive application of microprocessors and microcontrollers in consumer and industrial products. The microprocessor chip forms the heart of personal computers and workstations, and digital signal processing is the basis of modern telecommunications. Microcontrollers are found in everything from CD/MP3 players to refrigerators to washing machines to vacuum cleaners, and in today's luxury automobiles often more than 50 microprocessors work together to control the vehicle. In fact, as much as 40 to 50 percent of the total cost of luxury cars is projected to come from electronics in the near future.

The digital electronics market is dominated by far by **complementary MOS**, or **CMOS**, **technology**. However, as pointed out in previous chapters, the first successful manufacturing processes were developed for bipolar devices and the first integrated circuits utilized bipolar transistors. The rapid advance in the application of digital electronics was facilitated by circuit designers who developed early bipolar logic families called resistor-transistor logic (RTL) and

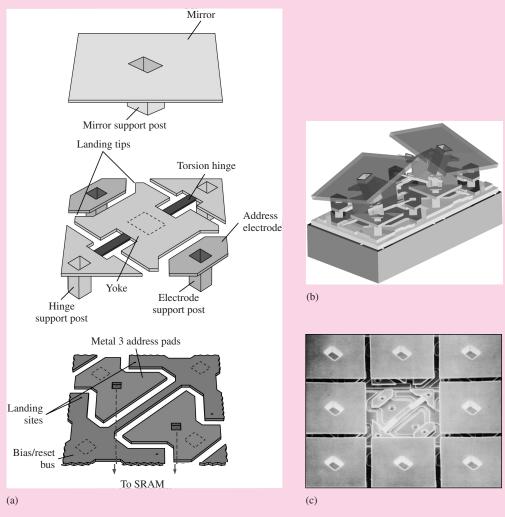

Intel Founders Andy Grove, Robert Noyce, and Gordon Moore with rubylith layout of 8080 microprocessor.

Photo Courtesy of Intel Corporation

Intel IA-64 Microprocessor employing more than 25M transistors.

Photo Courtesy of Intel Corporation

diode-transistor logic (DTL). These families were subsequently replaced with highly robust bipolar logic families including **transistor-transistor logic** (**TTL**) and **emitter-coupled logic** (**ECL**) that could be easily interconnected to form highly reliable digital systems. High-performance forms of TTL and ECL remain in use today.

It took almost a decade to develop viable MOS manufacturing processes. The first high-density MOS integrated circuits utilizing PMOS technology appeared around 1970. The landmark development of the microprocessor is attributed to Ted Hoff who convinced Intel to develop the 4-bit 4004 microprocessor chip containing approximately of 2300 transistors that was introduced in 1971.

As with many advances, work on single-chip processors started rapidly in research and development laboratories around the world. In the following 30 years, the industry went on to develop microprocessor chips of incredible complexity. As this edition is written, the IA-64 chip employing more than 25 million transistors has been introduced, and the ITRS projections in Chapter 1 predict microprocessors with more than a billion transistors will appear by the year 2010.

By the mid 1970s, PMOS was being rapidly replaced by the higher-performance NMOS technology. The Intel 8080, 8085, and 8086 were all implemented in NMOS logic. A significant advance in NMOS circuit performance was achieved with the introduction of the depletion-mode load device, and this work was formally recognized when Dr. Toshiaki Masuhara of Hitachi received the 1990 IEEE Solid-State Circuits Technical Field Award for this work.

But by the mid 1980s, power dissipation levels associated with NMOS microprocessors had reached unmanagable levels, and the industry made a transition to CMOS technology almost overnight. CMOS has remained the dominant technology since that time.

In this chapter, we begin our study of digital logic circuits with the introduction of a number of important concepts and definitions related to logic circuits. Then the chapter looks in detail at the design of MOS logic circuits built using only a single transistor type—either NMOS or PMOS—referred to as "single-channel technology." Complementary MOS (CMOS) logic, that uses both NMOS and PMOS transistors, is discussed in Chapter 7, and MOS memory and storage circuits are introduced in Chapter 8. Bipolar logic circuits are discussed in Chapter 9.

his chapter explores the requirements and general characteristics of digital logic gates. Subsequent chapters investigate the detailed implementation of logic gates in both MOS and bipolar technologies. The initial discussion in this chapter focuses on the characteristics of the inverter. Important logic levels associated with binary logic are defined, and the concepts of the voltage transfer characteristic and noise margin are introduced. Later, the temporal behavior and time delays of the gates are addressed. A review of Boolean algebra, used for representation and analysis of logic functions, is included, and simple AND gates, OR gates, and NAND gates are implemented using diode logic and bipolar transistors.

### **6.1 IDEAL LOGIC GATES**

We begin our discussion of logic gates by considering the characteristics of the ideal logical inverter. Although we cannot achieve the ideal behavior, the concepts and definitions form the basis for our study of actual circuit implementations of MOS and bipolar logic families in Chapters 7, 8, and 9.

In the discussions in this book, we limit consideration to binary logic, which requires only two discrete states for operation. In addition, the positive logic convention will be used throughout: The higher voltage level will correspond to a logic 1, and the lower voltage level will correspond to a logic 0.

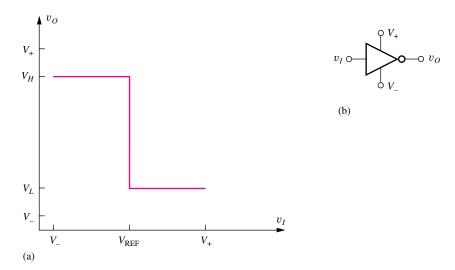

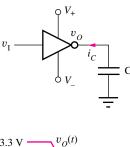

The logic symbol and **voltage transfer characteristic (VTC)** for an ideal inverter are given in Fig. 6.1. The positive and negative power supplies, shown explicitly as  $V_+$  and  $V_-$ , respectively, are not included in most logic diagrams. For input voltages  $v_I$  below the **reference voltage**  $V_{\text{REF}}$ , the output  $v_o$  will be in the **high logic level at the gate output**  $V_H$ . As the input voltage increases and exceeds  $V_{\text{REF}}$ , the output voltage changes abruptly to the **low logic level at the gate output**  $V_L$ . The output voltages corresponding to  $V_H$  and  $V_L$  generally fall between the supply voltages  $V_+$  and  $V_-$  but may not be equal to either voltage. For an input equal to  $V_+$  or  $V_-$ , the output does not necessarily reach either  $V_-$  or  $V_+$ . The actual levels depend on the individual logic family, and the reference voltage  $V_{\text{REF}}$  is determined by the internal circuitry of the gate.

In most digital designs, the power supply voltage is predetermined either by technology constraints or system-level power supply criteria. For example,  $V_+ = 5.0 \text{ V}$  (with  $V_- = 0$ ) represented

Figure 6.1 (a) Voltage transfer characteristic for an ideal inverter. (b) Inverter logic symbol.

the standard power supply for logic for many years. However, because of the power-dissipation, heat-removal, and breakdown-voltage limitations of advanced technology, a new power supply voltage equal to 3.3 V is in widespread use. In addition, many low-power systems must be designed to operate from battery voltages as low as 1.0 to 1.5 V, and many ICs now operate from supply voltages of 1.8 to 2.5 V.

### **6.2 LOGIC LEVEL DEFINITIONS AND NOISE MARGINS**

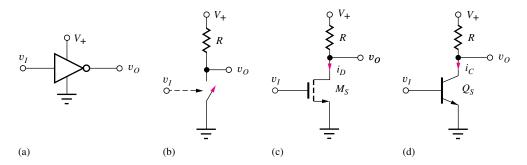

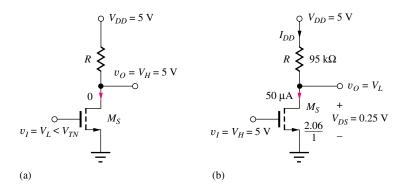

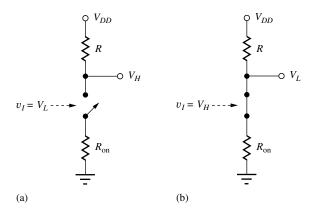

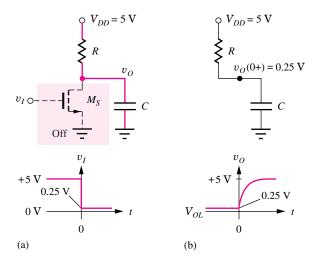

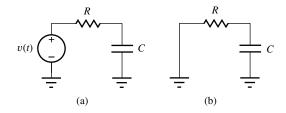

Now, let us look at electronic implementations of the inverter. Conceptually, the basic inverter circuit consists of a load resistor and a switch controlled by the input voltage  $v_I$ , as indicated in Fig. 6.2(b). When closed, the switch forces  $v_O$  to  $V_L$ , and when open, the resistor sets the output to  $V_H$ . In Fig. 6.2(b), for example,  $V_L = 0$  V and  $V_H = V_+$ .

Figure 6.2 (a) Inverter operating with power supplies of 0 V and  $V_+$ . (b) Simple inverter circuit comprising a load resistor and switch. (c) Inverter with NMOS transistor switch. (d) Inverter with BJT switch.

The voltage-controlled switch can be realized by either the MOS transistor in Fig. 6.2(c) or the bipolar transistor in Fig. 6.2(d). Transistors  $M_S$  and  $Q_S$  switch between two states: nonconducting or "off," and conducting or "on". Load resistor R sets the output voltage to  $V_H = V_+$  when switching transistor  $M_S$  or  $Q_S$  is off. If the input voltage exceeds the threshold voltage of  $M_S$  or the turn-on voltage of the base-emitter junction of  $Q_S$ , the transistors conduct a current that causes the output voltage to drop to  $V_L$ . When transistors are used as switches, as in Figs. 6.2(c) and (d),  $V_L \neq 0$  V. Detailed discussion of the design of these circuits appears later in this chapter and in Chapter 9.

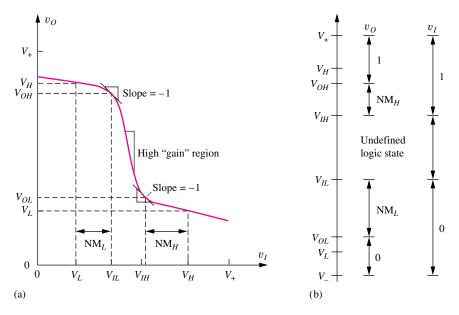

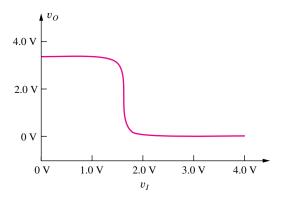

In the inverter circuit, the transition between  $V_H$  and  $V_L$  does not occur in the abrupt manner indicated in Fig. 6.1 but is more gradual, as indicated by the more realistic transfer characteristic shown in Fig. 6.3(a). A single, well-defined value of  $V_{\rm REF}$  does not exist. Instead, several additional input voltage levels are important.

When the input  $v_I$  is below the **input low-logic-level**  $V_{IL}$ , the output is defined to be in the high-output or 1 state. As the input voltage increases, the output voltage  $v_o$  falls until it reaches the low output or 0 state as  $v_I$  exceeds the voltage of the **input high-logic-level**  $V_{IH}$ . The input voltages  $V_{IL}$  and  $V_{IH}$  are defined by the points at which the slope of the voltage transfer characteristic equals -1. Voltages below  $V_{IL}$  are reliably recognized as logic 0s at the input of a logic gate, and voltages above  $V_{IH}$  are recognized reliably as logic 1s at the input. Voltages corresponding to the region between  $V_{IL}$  and  $V_{IH}$  do not represent valid logic input levels and generate logically indeterminate output voltages. The transition region of high negative slope between these two points represents an undefined logic state. The voltages labeled as  $V_{OL}$  and

<sup>&</sup>lt;sup>1</sup> This region corresponds to a region of relatively high voltage gain. See Probs. 6.6 and 6.7.

Figure 6.3 (a) Voltage transfer characteristic for the inverters in Fig. 6.2 with  $V_{-} = 0$ . (b) Voltage levels and logic state relationships for positive logic.

$V_{OH}$  represent the gate output voltages at the -1 slope points and correspond to input levels of  $V_{IH}$  and  $V_{IL}$ , respectively.

In Part III of this book, we will find that the region of the VTC with a high negative slope between  $V_{IL}$  and  $V_{IH}$  corresponds to a large "voltage gain," and we actually use this region for amplification of analog signals. The gain is the slope of the voltage transfer characteristic. The higher the gain, the narrower will be the voltage range corresponding to the undefined logic state in Fig. 6.3.

An alternate representation of the voltages and voltage ranges appears in Fig. 6.3(b), along with quantities that represent the voltage noise margins. The various terms are defined more fully next.

### **6.2.1** LOGIC VOLTAGE LEVELS

- $V_L$  The nominal voltage corresponding to a low-logic state at the output of a logic gate for  $v_I = V_H$ . Generally,  $V_- \leq V_L$ .

- $V_H$  The nominal voltage corresponding to a high-logic state at the output of a logic gate for  $v_I = V_L$ . Generally,  $V_H \leq V_+$ .

- $V_{IL}$  The maximum input voltage that will be recognized as a low input logic level.

- $V_{IH}$  The minimum input voltage that will be recognized as a high input logic level.

- $V_{OH}$  The output voltage corresponding to an input voltage of  $V_{IL}$ .

- $V_{OL}$  The output voltage corresponding to an input voltage of  $V_{IH}$ .

For subsequent discussions of MOS logic,  $V_{-}$  will usually be taken to be 0 V, and  $V_{+}$  will be either 3.3 V or 5 V. These voltages are also commonly used in bipolar logic. However, other values are possible. For example, emitter-coupled logic, discussed in Chapter 9 on bipolar logic design, has historically used  $V_{+} = 0$  V and  $V_{-} = -5.2$  V or -4.5 V, and new low-power ECL gates have been developed to operate with a total supply voltage span of only 2 V.

### 6.2.2 Noise Margins

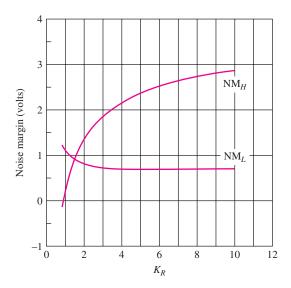

The noise margin in the high state  $NM_H$  and noise margin in the low state  $NM_L$  represent "safety margins" that prevent the gate from producing erroneous logic decisions in the presence of noise sources. The noise margins are needed to absorb voltage differences that may arise between the outputs and inputs of various logic gates due to a variety of sources. These may be extraneous signals coupled into the gates or simply parameter variations between gates in a logic family.

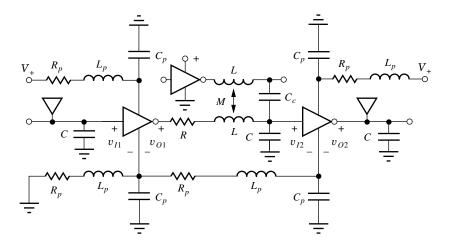

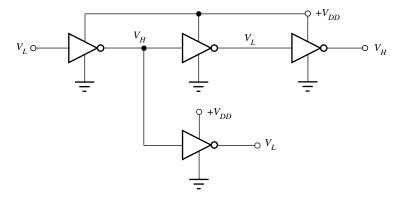

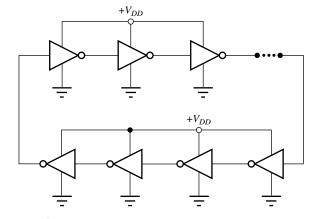

Figure 6.4 shows several interconnected inverters and illustrates why noise margin is important. The signal and power interconnections on a printed circuit board or integrated circuit, which we most often draw as zero resistance wires (or short circuits), really consist of distributed *RLC* networks. In Fig. 6.4 the output of the first inverter,  $v_{O1}$ , and the input of the second inverter,  $v_{I2}$ , are not necessarily equal. As logic signals propagate from one logic gate to the next, their characteristics become degraded by the resistance, inductance, and capacitance of the interconnections. Rapidly switching signals may induce transient voltages and currents directly onto nearby signal nodes and lines through capacitive and inductive coupling indicated by  $C_c$  and M. In an RF environment, the interconnections may even act as small antennae that can couple additional extraneous signals into the logic circuitry. Similar problems occur in the power distribution network. Both direct current and transient currents during gate switching generate voltage drops across the various components  $(R_p, L_p, C_p)$  of the power distribution network.

Figure 6.4 Inverters embedded in a signal and power and distribution network.

There are a number of different ways to define the noise margin [1–3] of a logic gate. In this text, we will use a definition based on the input and output voltages at the -1 slope points on the inverter voltage transfer characteristic, as identified in Fig. 6.3:

$NM_L$  The noise margin associated with a low input level is defined by

$$NM_L = V_{IL} - V_{OL} \tag{6.1}$$

$NM_H$  The noise margin associated with a high input level is defined by

$$NM_H = V_{OH} - V_{IH} (6.2)$$

The noise margins represent the voltages necessary to upset the logic levels in a long chain (actually an infinite chain) of inverters, or in the cross-coupled flip-flop storage elements that we explore in Chapter 8. The definitions in Eqs. (6.1) and (6.2) can be shown [1-3] to maximize the sum of

the two noise margins.<sup>2</sup> These definitions provide a reasonable metric for comparing the noise margins of different logic families and are relatively easy to understand and calculate. The method for actually finding the worst-case noise margins for a logic family uses a graphical approach described in [1]. However, it is much more cumbersome to describe and difficult to implement.

The noise margins also help absorb parameter variations that occur between individual logic gates. During manufacture, there will be unavoidable variations in device and circuit parameters, and variations will occur in the power supply voltages and operating temperature during application of the logic circuits. Normally, the logic manufacturer specifies worst-case values for  $V_H$ ,  $V_L$ ,  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$ . In our analysis, however, we will generally restrict ourselves to finding nominal values of these voltages.

**EXERCISE:** A certain TTL gate has the following values for its logic levels:  $V_{OH} = 3.6 \text{ V}$ ,  $V_{OL} = 0.4 \text{ V}$ ,  $V_{IH} = 2.0 \text{ V}$ ,  $V_{IL} = 0.8 \text{ V}$ . What are the noise margins for this TTL gate?

**ANSWERS:**  $NM_H = 1.6 \text{ V}; NM_L = 0.4 \text{ V}$

### 6.2.3 LOGIC GATE DESIGN GOALS

As we explore the design of logic gates, we should keep in mind a number of goals.

- 1. From Fig. 6.1, we see that the ideal logic gate is a highly nonlinear device that attempts to quantize the input signal into two discrete output levels. In the actual gate in Figs. 6.2 and 6.3, we should strive to minimize the width of the undefined input voltage range, and the noise margins should generally be as large as possible.

- Logic gates should be unidirectional in nature. The input should control the output to produce a well-defined logic function. Voltage changes at the output of a gate should not affect the input side of the circuit.

- 3. The logic levels must be regenerated as the signal passes through the gate. In other words, the voltage levels at the output of one gate must be compatible with the input voltage levels of the same or similar logic gates.

- 4. The output of one gate should also be capable of driving the inputs of more than one gate. The number of inputs that can be driven by the output of a logic gate is called the **fan-out** capability of that gate. The term **fan in** refers to the number of input signals that may be applied to the input of a gate.

- 5. In most design situations, the logic gate should consume as little power (and area in an IC design) as needed to meet the speed requirements of the design.

### 6.3 DYNAMIC RESPONSE OF LOGIC GATES

In today's environment, even the general public is familiar with the seemingly endless increase in logic performance as we are bombarded with marketing of the latest microprocessors in terms of their clock frequencies, 500 MHz, 750 MHz, 1 GHz, and so on. The clock rate of a processor is ultimately set by the dynamic performance of the individual logic circuits. In engineering terms, the time domain performance of a logic family is cast in terms of its average propagation delay, rise time, and fall time as defined in this section.

<sup>&</sup>lt;sup>2</sup> In some cases, this simple definition can yield a negative value for one of the noise margins.

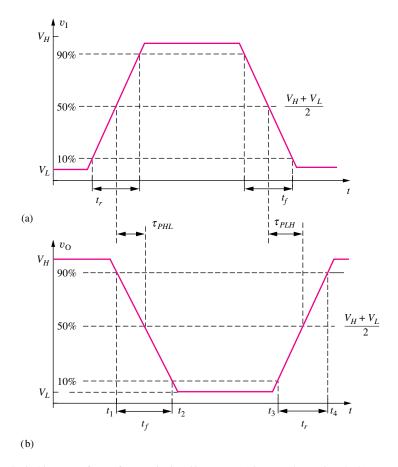

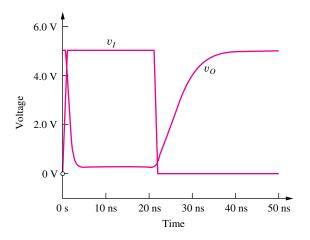

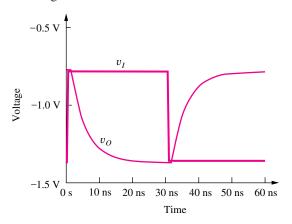

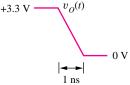

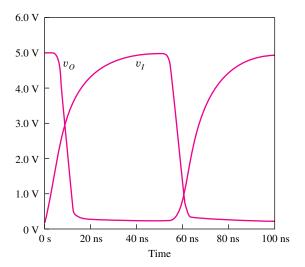

**Figure 6.5** Switching waveforms for an *idealized* inverter: (a) input voltage signal, (b) output voltage waveform.

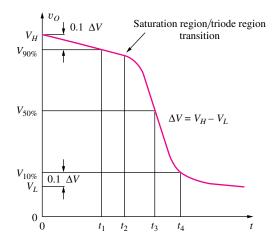

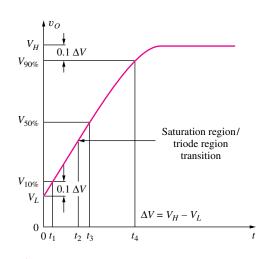

Figure 6.5 shows idealized time domain waveforms for an inverter. The input and output signals are switching between the two static logic levels  $V_{OL}$  and  $V_{OH}$ . Because of capacitances in the circuits, the waveforms exhibit nonzero rise and fall times, and propagation delays occur between the switching times of the input and output waveforms.

### 6.3.1 RISE TIME AND FALL TIMES

The **rise time**  $t_r$  for a given signal is defined as the time required for the signal to make the transition from the "10 **percent" point** to the "90 **percent" point** on the waveform, as indicated in Fig. 6.5. The **fall time**  $t_f$  is defined as the time required for the signal to make the transition between the 90 percent point and the 10 percent point on the waveform. The voltages corresponding to the 10 percent and 90 percent points are defined in terms of  $V_L$  and  $V_H$  and the logic swing  $\Delta V$ :

$$V_{10\%} = V_L + 0.1 \,\Delta V$$

$$V_{90\%} = V_L + 0.9 \,\Delta V = V_H - 0.1 \,\Delta V$$

(6.3)

where  $\Delta V = V_H - V_L$ . Rise and fall times usually have unequal values; the characteristic shapes of the input and output waveforms also differ.

### 6.3.2 Propagation Delay

Propagation delay is measured as the difference in time between the input and output signals reaching the "50 percent" points in their respective transitions. The 50 percent point is the voltage level corresponding to one-half the total transition between  $V_H$  and  $V_L$ :

$$V_{50\%} = \frac{V_H + V_L}{2} \tag{6.4}$$

The **propagation delay** on the **high-to-low output transition** is  $\tau_{PHL}$  and that of the **low-to-high transition** is  $\tau_{PLH}$ . In the general case, these two delays will not be equal, and the **average propagation delay**  $\tau_P$  is defined by

$$\tau_P = \frac{\tau_{PLH} + \tau_{PHL}}{2} \tag{6.5}$$

Average propagation delay is one figure of merit that is commonly used to compare the performance of different logic families. In Chapters 6, 7, and 9 we explore the propagation delays for various MOS and bipolar logic circuits.

**EXERCISE:** Suppose the waveforms in Fig. 6.5 are those of an ECL gate with  $V_L = -2.6$  V and  $V_H = -0.6$  V, and  $t_1 = 100$  ns,  $t_2 = 105$  ns,  $t_3 = 150$  ns, and  $t_4 = 153$  ns. What are the values of  $V_{10\%}$ ,  $V_{90\%}$ ,  $V_{50\%}$ ,  $t_r$ , and  $t_f$ ?

**ANSWERS:** -2.4 V; -0.8 V; -1.6 V; 3 ns; 5 ns

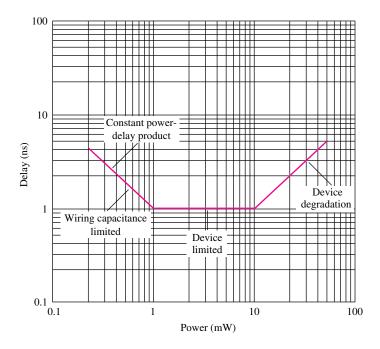

### 6.3.3 POWER-DELAY PRODUCT

The overall performance of a logic family is ultimately determined by how much energy is required to change the state of the logic circuit. The traditional metric for comparing various logic families is the power-delay product, which tells us the amount of energy that is required to perform a basic logic operation.

Figure 6.6 shows the behavior of the average propagation delay of a general logic gate versus the average power supplied to the gate. The power consumed by a gate can be changed by increasing or decreasing the sizes of the transistors and resistors in the gate or by changing the power supply voltage. At low power levels, gate delay is dominated by intergate wiring capacitance, and the delay decreases as power increases. As device size and power are increased further, circuit delay becomes limited by the inherent speed of the electronic switching devices, and the delay becomes independent of power. In bipolar logic technology, the properties of the transistors begin to degrade at even higher power levels, and the delay can actually become worse as power increases further, as indicated in Fig. 6.6.

In the low power region, the propagation delay decreases in direct proportion to the increase in power. This behavior corresponds to a region of constant **power-delay product (PDP)**,

$$PDP = P\tau_P \tag{6.6}$$

in which P is the average power dissipated by the logic gate. The PDP represents the energy (Joules) required to perform a basic logic operation and is another figure of merit widely used to compare logic families.

Figure 6.6 Logic gate delay versus power dissipation.

Early logic families had power-delay products of 10 to 100 pJ (1 pJ =  $10^{-12}$  J), whereas many of today's IC logic families now have PDPs in the 10 to 100 fJ range (1 fJ =  $10^{-15}$  J). It has been estimated that the minimum energy required to reliably differentiate two logic states is on the order of (ln 2)kT, which is approximately  $4 \times 10^{-20}$  J at room temperature [4]. Thus even today's best logic families have power-delay products that are many orders of magnitude from the ultimate limit [5].

**EXERCISE:** (a) What is the power-delay product at low power for the logic gate characterized by Fig. 6.6? (b) What is the PDP at P = 3 mW? (c) At 20 mW?

**Answers:** 1 pJ; 3 pJ; 40 pJ

### 6.4 REVIEW OF BOOLEAN ALGEBRA

In order to be able to effectively deal with logic system analysis and design, we need a mathematical representation for networks of logic gates. Fortunately, way back in 1849, G. Boole [6] presented a powerful mathematical formulation for dealing with logical thought and reasoning, and the formal algebra we use today to manipulate binary logic expressions is known as **Boolean algebra**. Tables 6.1 to 6.6 and the following discussion summarize Boolean algebra.

Table 6.1 lists the basic logic operations that we need. The logic function at the gate output is represented by variable Z and is a function of logical input variables A and B: Z = f(A, B). To perform general logic operations, a logic family must provide logical inversion (NOT) plus at least one other function of two input variables, such as the OR or AND functions. We will find in Chapter 7 that NMOS logic can easily be used to implement **NOR gates** as well as **NAND gates**, and in Chapter 9 we will see that the basic TTL gate provides a NAND function whereas

| TABLE 6.1                |

|--------------------------|

| Basic Boolean Operations |

|           | · · · · · · ·                              |

|-----------|--------------------------------------------|

|           |                                            |

| OPERATION | BOOLEAN REPRESENTATION                     |

| NOT       | $Z = \overline{A}$                         |

| OR        | Z = A + B                                  |

| AND       | $Z = A \cdot B = AB$                       |

| NOR       | $Z = \overline{A + B}$                     |

| NAND      | $Z = \overline{A \cdot B} = \overline{AB}$ |

|           |                                            |

| TABLE 6.2                |   |

|--------------------------|---|

| NOT (Inverter) Truth Tab | e |

| Α | $Z=\overline{A}$ |

|---|------------------|

| 0 | 1                |

| 1 | 0                |

| IABLE 0.3 |               |           |

|-----------|---------------|-----------|

| OR G      | ate Truth Tab | le        |

|           |               |           |

| Α         | В             | Z = A + 1 |

| on oute fruit fubic |   |           |  |  |

|---------------------|---|-----------|--|--|

| Α                   | В | Z = A + B |  |  |

| 0                   | 0 | 0         |  |  |

| 0                   | 1 | 1         |  |  |

| 1                   | 0 | 1         |  |  |

| 1                   | 1 | 1         |  |  |

|                     |   |           |  |  |

| TABLE 6.4                   |

|-----------------------------|

| <b>AND Gate Truth Table</b> |

| Α | В | Z = AB |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

OR/NOR logic is provided by the basic ECL gate. Note in Table 6.1 that the NOT function is equivalent to the output of either a single input NOR gate or NAND gate.

**Truth tables** and logic symbols for the five functions in Table 6.1 appear in Tables 6.2 to 6.6 and Figs. 6.7 to 6.9. The truth table presents the output Z for all possible combinations of the input variables A and B. The inverter,  $Z = \overline{A}$ , has a single input, and the output represents the logical inversion or complement of the input variable, as indicated by the overbar (Table 6.2; Fig. 6.7).

Tables 6.3 and 6.4 are the truth tables for a two-input **OR gate** and a two-input **AND gate**, respectively, and the corresponding logic symbols appear in Fig. 6.8. The OR operation is indicated by the + symbol; its output Z is a 1 when either one or both of the input variables A or B is a 1. The output is a 0 only if both inputs are 0. The AND operation is indicated by the • symbol, as in  $A \cdot B$ , or in a more compact form as simply AB, and the output Z is a 1 only if both the input variables A and B are in the 1 state. If either input is 0, then the output is 0. We shall use AB to represent A AND B throughout the rest of this text.

Figure 6.7 Inverter symbol.

$$\begin{array}{cccc}

A & \bigcirc & & \\

B & \bigcirc & & \\

\end{array}$$

(a)

$$\begin{array}{cccc}

Z = A + B \\

\bigcirc & & \\

\end{array}$$

Figure 6.8 (a) OR gate symbol. (b) AND gate symbol.

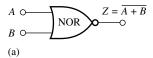

Figure 6.9 (a) NOR gate symbol. (b) NAND gate symbol.

| TABLE 6.5 NOR Gate Truth Table |                  |                                   |  |  |

|--------------------------------|------------------|-----------------------------------|--|--|

| <b>A</b><br>0                  | <b>B</b><br>0    | $Z = \overline{A + B}$ 1          |  |  |

| 0                              | 1                | 0                                 |  |  |

| 1                              | 0                | 0                                 |  |  |

| 1                              | 1                | 0                                 |  |  |

|                                | <b>NOR 6 A</b> 0 | NOR Gate Truth Table  A B 0 0 0 1 |  |  |

| TABLE 6.6<br>NAND Gate Truth Table |   |                     |  |

|------------------------------------|---|---------------------|--|

| Α                                  | В | $Z = \overline{AB}$ |  |

| 0                                  | 0 | 1                   |  |

| 0                                  | 1 | 1                   |  |

| 1                                  | 0 | 1                   |  |

| 1                                  | 1 | 0                   |  |

Tables 6.5 and 6.6 are the truth tables for the two-input NOR gate and the two-input NAND gate, respectively, and the logic symbols appear in Fig. 6.9. These functions represent the complements of the OR and AND operations — that is, the OR or AND operations followed by logical inversion. The NOR operation is represented as  $Z = \overline{A + B}$ , and its output Z is a 1 only if both inputs are 0. For the NAND operation,  $Z = \overline{AB}$ , output Z is a 1 except when both the input variables A or B are in the 1 state.

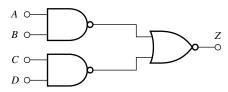

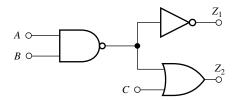

In this chapter and Chapter 8, we will find that a major advantage of MOS logic is its capability to readily form more complex logic functions, particularly logic expressions represented in a complemented **sum-of-products** form:

$$Z = \overline{AB + CD + E}$$

or  $Z = \overline{ABC + DE}$  (6.7)

The Boolean identities that are shown in Table 6.7 can be very useful in finding simplified logic expressions, such as those expressions in Eq. (6.7). This table includes the identity operations as well as the basic commutative, associative, and distributive laws of Boolean algebra.

**TABLE 6.7**Useful Boolean Identities

| A + 0 = A $A + B = B + A$                               | $A \cdot 1 = A$ $AB = BA$                                | Identity operation Commutative law |

|---------------------------------------------------------|----------------------------------------------------------|------------------------------------|

| A + B = B + A $A + (B + C) = (A + B) + C$               | AB = BA $A(BC) = (AB)C$                                  | Associative law                    |

| $A + BC = (A + B)(A + C)$ $A + \overline{A} = 1$        | $A(B+C) = AB + AC$ $A \cdot \overline{A} = 0$            | Distributive law Complements       |

| A + A = 1 $A + A = A$                                   | $A \cdot A = 0$<br>$A \cdot A = A$                       | Idempotency                        |

| $\frac{A+1=1}{\overline{A}+\overline{B}=\overline{AB}}$ | $\frac{A \cdot 0 = 0}{AB = \overline{A} + \overline{B}}$ | Null elements DeMorgan's theorem   |

| A + B = AB                                              | MB = M + B                                               | Delviorgan's theorem               |

#### **EXAMPLE 6.1** LOGIC EXPRESSION SIMPLIFICATION

Here is an example of the use of Boolean identities to simplify a logic expression.

**PROBLEM** Use the Boolean relationships in Table 6.7 to show that the expression

$$Z = A\overline{B}C + ABC + \overline{A}BC$$

can be reduced to  $Z = (A + B)C$ .

**SOLUTION Known Information and Given Data:** Two expressions for *Z* just given; Boolean identities in Table 6.7

**Unknowns:** Proof that Z is equivalent to (A + B)C

**Approach:** Apply various identities from Table 6.7 to simplify the formula for Z

**Assumptions:** None

**Analysis:**

$$Z = A\overline{B}C + ABC + \overline{A}BC$$

$$Z = A\overline{B}C + ABC + ABC + \overline{A}BC \qquad \text{using } ABC = ABC + ABC$$

$$Z = A(\overline{B} + B)C + (\overline{A} + A)BC \qquad \text{using distributive law}$$

$$Z = A(1)C + (1)BC \qquad \text{using } (\overline{B} + B) = (B + \overline{B}) = 1$$

$$Z = AC + BC \qquad \text{since } A(1)C = AC(1) = AC$$

$$Z = (A + B)C \qquad \text{using distributive law}$$

**Check of Results:** We have reached the desired answer. A double check indicates the sequence of steps appears valid.

**EXERCISE:** Simplify the logic expression Z = (A + B)(B + C)

**ANSWER:** Z = B + AC

### 6.5 DIODE LOGIC AND DTL

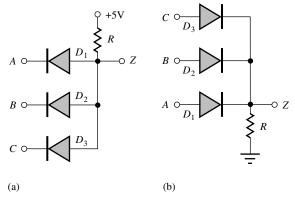

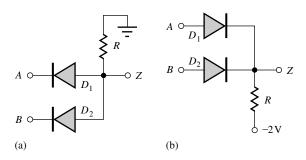

**Diode logic** is one of the simplest circuit techniques that can be used to implement the AND and OR functions. Although of somewhat limited utility, diode logic provides a simple introduction to logic circuit implementation and can be used in circuit design to logically combine several input signals.

### 6.5.1 DIODE OR GATE

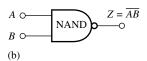

Figure 6.10 is the circuit diagram of a simple diode OR gate along with circuit voltages for the case A=1 or 5 V and B=0 or 0 V. In Fig. 6.10(b), diode  $D_1$  is conducting, diode  $D_2$  is reverse-biased, and the output voltage is one diode voltage drop below the 5 V input at A. Using

Figure 6.10 (a) Diode OR gate. (b) OR gate with A = 1 and B = 0.

the constant-voltage-drop model from Chapter 3 with  $V_{\rm on}=0.6$  V,  $v_0=5$  V -0.6 V =4.4 V and Z=1. Although the output voltage is not equal to the full 5-V input level, 4.4 V is usually sufficiently large to be interpreted as a logical 1. If at least one of the inputs in the circuit in Fig. 6.10 is at +5 V, then the output of this gate will be at 4.4 V. If both inputs are at 0 V, then  $D_1$  and  $D_2$  will both be nonconducting and  $v_0=0$ . Thus, the diode circuit in Fig. 6.10 is a basic form of OR logic.

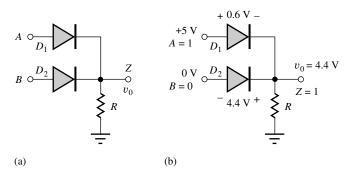

### 6.5.2 DIODE AND GATE

By reversing the diodes and power supply, as in Fig. 6.11, the circuit becomes an AND gate. In Fig. 6.11(b), we again look at the circuit for the case A = 1 (5 V) and B = 0 (0 V). Diode  $D_1$  is now reverse-biased, diode  $D_2$  is conducting, and the output voltage is one diode voltage drop above ground potential:

$$v_0 = (0 + 0.6) \text{ V} = 0.6 \text{ V}$$

and  $Z = 0$

Although the output voltage is not equal to 0 V, the 0.6-V level is sufficiently low to be interpreted as a logical 0. If either one or both of the inputs is at 0 V, then the output of the gate is 0.6 V. Only if both inputs are at +5 V will the output also be at +5 V, corresponding to Z=1. Thus, the circuit in Fig. 6.11 functions as a basic AND gate.

Figure 6.11 (a) Diode AND gate. (b) AND gate with A = 1, B = 0, and Z = 0.

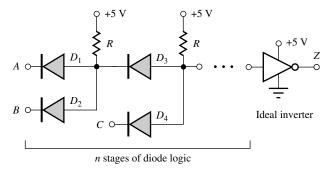

Although the diode OR and AND gates provide simple implementations of their respective logic function, they both suffer from the same problem. The gates do not satisfy design goal 3 discussed in Sec. 6.2 because the logic levels are not regenerated at the output of the gate. When several similar gates are connected in series, the output level is degraded one diode drop by each gate in the chain. If too many diode logic gates are cascaded, then the output voltage no longer represents the proper binary state. However, there are often cases where the circuit designer would like to form the AND or OR combination of several logical variables in a simple control circuit, and diode logic will suffice.

### 6.5.3 A DIODE-TRANSISTOR LOGIC (DTL) GATE

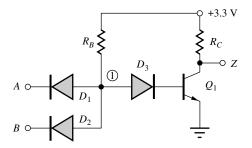

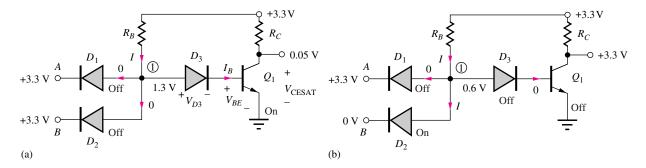

The level-restoration problem associated with diode logic can be solved by adding a diode and transistor to form the **diode-transistor logic** (DTL) gate shown schematically in Fig. 6.12. We will analyze bipolar logic gates in detail in Chapter 9; here is a brief overview of the operation of this gate.

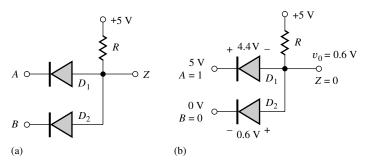

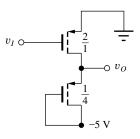

The situation in Fig. 6.13(a) corresponds to the case in which both inputs are in the logical 1 state,  $V_H = V_+ = 3.3$  V. In this particular circuit, diodes  $D_1$  and  $D_2$  are both off, whereas  $D_3$  and  $Q_1$  are on. Node 1 is at 1.3 V:

$$V_1 = V_{D3} + V_{BE} = 0.6 \text{ V} + 0.7 \text{ V} = 1.3 \text{ V}$$

Figure 6.12 A two-input diode-transistor logic (DTL) NAND gate.

Figure 6.13 A diode-transistor NAND gate: (a) both inputs high, (b) one input low.

The current I through resistor  $R_B$  and diode  $D_3$  becomes the base current  $I_B$  of transistor  $Q_1$ . The value of  $I_B$  is designed to cause  $Q_1$  to saturate so that  $v_O = V_{\text{CESAT}}$  (for example, 0.05 to 0.1 V). In Fig. 6.13(b), input B is now at 0 V, corresponding to a logical 0. Diode  $D_2$  is conducting, holding node 1 at 0.6 V. Now diode  $D_3$  and transistor  $Q_1$  must both be off, because the voltage at node 1 is now less than the two diode voltage drops required to turn on both  $D_3$  and  $Q_1$ . The base current of  $Q_1$  is now zero;  $Q_1$  will be off with  $I_C = 0$ , and the output voltage will be at +3.3 V, corresponding to a logical 1. A similar situation holds for the circuit if both inputs are low. The truth table for this gate is identical to Table 6.6. The DTL circuit represents a two-input NAND gate with  $Z = \overline{AB}$ .

**EXERCISE:** What is the base current in transistor  $Q_1$  in Fig. 6.13(a) if  $R_B = 100 \text{ k}\Omega$ ?

Answer: 20 μA

### 6.6 NMOS LOGIC DESIGN

The rest of Chapter 6 focuses on understanding the design of MOS logic gates that use only *n*-channel MOS transistors (NMOS logic) or *p*-channel MOS transistors (PMOS logic). Study of these circuits employing **single-channel technology** provides a background for understanding many important logic circuit concepts as well as the improvements gained by going to CMOS circuitry, which is the topic for Chapter 7. The discussion begins by investigating the design of the MOS inverter in order to gain an understanding of its voltage transfer characteristic and noise margins. Inverters with four different load configurations are considered: the resistor load,

saturated load, linear load, and depletion-mode load circuits. NOR, NAND, and more complex logic gates can be easily designed as simple extensions of the reference inverter designs. Later, the rise time, fall time, and propagation delays of the gates are analyzed.

The drain current of the MOS device depends on its gate-source voltage  $v_{GS}$ , drain-source voltage  $v_{DS}$ , and source-bulk voltage  $v_{SB}$ , and on the device parameters, which include the transconductance parameter  $K'_n$ , threshold voltage  $V_{TN}$ , and width-to-length or W/L ratio. The power supply voltage constrains the range of  $v_{GS}$  and  $v_{DS}$ , and the technology sets the values of  $K'_n$  and  $V_{TN}$ . Thus, the circuit designer's job is to choose the circuit topology and the W/L ratios of the MOS transistors to achieve the desired logic function.

In most logic design situations, the power supply voltage is predetermined by either technology reliability constraints or system-level criteria. For example, as mentioned in Sec. 6.1,  $V_{DD}^3 = 5.0 \text{ V}$  has been the standard power supply for logic for many years. However, a new 3.3-V power supply level is now gaining widespread use as well. In addition, many portable low-power systems, such as cell phones and PDAs, must operate from battery voltages as low as 1.0 to 1.5 V.

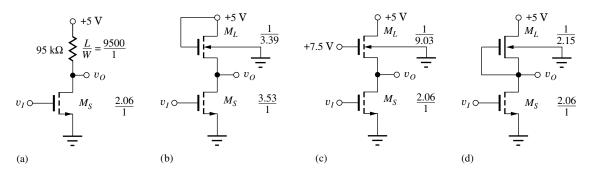

We begin our study of MOS logic circuit design by considering the detailed design of the NMOS inverter with the resistor load that was introduced in Chapter 5. Although we will seldom use this exact circuit, it provides a good basis for understanding operation of the basic logic gate. In integrated logic circuits, the load resistor occupies too much silicon area, and is replaced by a second NMOS transistor. This "load device" can be connected in three different configurations called the saturated load, linear load, and depletion-mode load circuits. We will explore the design of the NMOS load configurations in detail in this and Secs. 6.7 through 6.10.

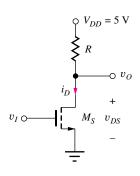

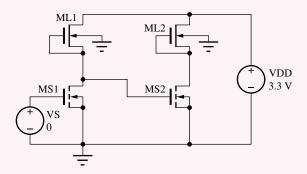

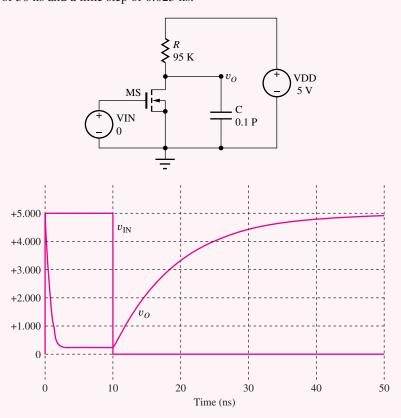

### 6.6.1 NMOS INVERTER WITH RESISTIVE LOAD

Complex digital systems can consist of millions of logic gates, and it is helpful to remember that each individual logic gate is generally interconnected in a larger network. The output of one logic gate drives the input of another logic gate, as shown schematically by the four inverters in Fig. 6.14. Thus, a gate has  $v_O = V_H$  when an input voltage  $v_I = V_L$  is applied to its input, and vice versa. For MOS design, we first need to find  $V_H$  and then apply it as an input to the gate in order to determine  $V_L$ .

The basic inverter circuit shown in Fig. 6.15 consists of an NMOS switching device  $M_S$  designed to force  $v_O$  to  $V_L$  and a **resistor load** element to "pull" the output up toward the power supply  $V_{DD}$ . The NMOS transistor is designed to switch between the triode region for  $v_I = V_H$  and the cutoff (nonconducting) state for  $v_I = V_L$ . The circuit designer must choose the values of the load resistor R and the W/L ratio of **switching transistor**  $M_S$  so the inverter meets a set of design specifications. In this case, these two design variables permit us to choose the  $V_L$  level and set the total power dissipation of the logic gate.

Let us explore the inverter operation by considering the requirements for the design of such a logic gate. Writing the equation for the output voltage, we find

$$v_O = v_{DS} = V_{DD} - i_D R (6.8)$$

When the input voltage is at a low state,  $v_I = V_L$ ,  $M_S$  should be cut off, with  $i_D = 0$ , so that

$$v_O = V_{DD} = V_H \tag{6.9}$$

Thus, in this particular logic circuit, the value of  $V_H$  is set by the power supply voltage  $V_{DD} = 5$  V.

$<sup>^3</sup>$   $V_{DD}$  and  $V_{SS}$  have traditionally been used to denote the positive and negative power supply voltages in MOS circuits.

Figure 6.14 A network of inverters.

Figure 6.15 NMOS inverter with resistive load.

**Figure 6.16** Inverters in the (a)  $v_I = V_L(0)$  and (b)  $v_I = V_H(1)$  logic states.

To ensure that transistor  $M_S$  is cut off when the input is equal to  $V_L$ , as in Fig. 6.16(a), the gate-source voltage of  $M_S$  ( $v_{GS} = V_L$ ) must be less than its threshold voltage  $V_{TN}$ . For  $V_{TN} = 1$  V, a normal design point would be for  $V_L$  to be in the range of 25 to 50 percent of  $V_{TN}$  or 0.25 to 0.50 V to ensure adequate noise margins. Let us assume a design value of  $V_L = 0.25$  V.

#### DESIGN OF VL

To ensure that switching transistor  $M_S$  is cut off when the input is in the low logic state,  $V_L$  is designed to be 25 to 50 percent of the threshold voltage of switch  $M_S$ . This choice also provides a reasonable value for noise margin  $NM_L$ .

### **6.6.2** Design of the W/L Ratio of $M_S$

The value of W/L required to set  $V_L = 0.25$  V can be calculated if we know the parameters of the MOS device. For now, the values  $V_{TN} = 1$  V and  $K'_n = 25 \times 10^{-6}$  A/V<sup>2</sup> will be used. In addition, we need to know a value for the desired operating current of the inverter. The current is determined by the permissible power dissipation of the NMOS gate when  $v_O = V_L$ . Using P = 0.25 mW (see

Probs. 6.44 and 6.45),<sup>4</sup> the current in the gate can be found from  $P = V_{DD} \times I_{DD}$ . For our circuit,

$$0.25 \times 10^{-3} = 5 \times I_{DD}$$

or  $I_{DD} = 50 \,\mu\text{A} = i_D$

Now we can determine the value for the W/L ratio of the NMOS switching device from the MOS drain current expression using the circuit conditions in Fig. 6.16(b). In this case, the input is set equal to  $V_H = 5$  V, and the output of the inverter should then be at  $V_L$ . The expression for the drain current in the triode region of the device is used because  $v_{GS} - V_{TN} = 5$  V - 1 V = 4 V, and  $v_{DS} = V_L = 0.25$  V, yielding  $v_{DS} < v_{GS} - V_{TN}$ .

$$i_D = K'_n \left(\frac{W}{L}\right)_S (v_{GS} - V_{TN} - 0.5v_{DS}) v_{DS}$$

(6.10)

or

$$5 \times 10^{-5} \text{ A} = \left(25 \times 10^{-6} \frac{\text{A}}{\text{V}^2}\right) \left(\frac{W}{L}\right)_S (5 \text{ V} - 1 \text{ V} - 0.125 \text{ V})(0.25 \text{ V})$$

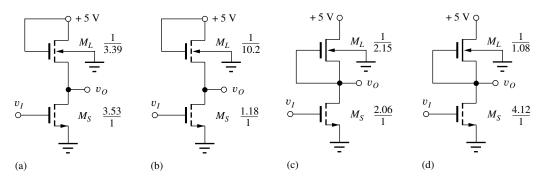

Solving Eq. (6.10) for  $(W/L)_S$  gives  $(W/L)_S = 2.06/1$ .

### 6.6.3 LOAD RESISTOR DESIGN

The value of the load resistor R is chosen to limit the current when  $v_O = V_L$  and is found from

$$R = \frac{V_{DD} - V_L}{i_D} = \frac{(5 - 0.25) \text{ V}}{5 \times 10^{-5} \text{ A}} = 95 \text{ k}\Omega$$

(6.11)

These design values are shown in the circuit in Fig. 6.16(b).

**EXERCISE:** Redesign the logic gate in Fig. 6.16 to operate at a power of 0.5 mW while maintaining  $V_L = 0.25$  V.

**ANSWER:**  $(W/L)_S = 4.12/1$ ;  $R = 47.5 \text{ k}\Omega$

### 6.6.4 LOAD-LINE VISUALIZATION

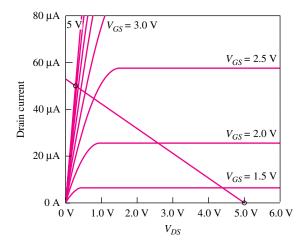

An important way to visualize the operation of the inverter is to draw the load line on the MOS transistor output characteristics as in Fig. 6.17. Equation (6.8), repeated here, represents the equation for the load line:

$$v_{DS} = V_{DD} - i_D R$$

When the transistor is cut off,  $i_D = 0$  and  $v_{DS} = V_{DD} = 5$  V, and when the transistor is on, the MOSFET is operating in the triode region, with  $v_{GS} = V_H = 5$  V and  $v_{DS} = v_O = V_L = 0.25$  V. The MOSFET switches between the two operating points on the load line, as indicated by the circles in Fig. 6.17. At the right-hand end of the load line, the MOSFET is cut off. At the Q-point near the left end of the load line, the MOSFET represents a relatively low resistance, and the current is determined primarily by the load resistance. (Note how the Q-point is nearly independent of  $v_{GS}$ .)

<sup>&</sup>lt;sup>4</sup> It would be worth exploring these problems before continuing.

Figure 6.17 MOSFET output characteristics and load line.

### DESIGN OF AN INVERTER WITH RESISTIVE LOAD

**DESIGN** EXAMPLE 6.2

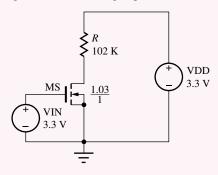

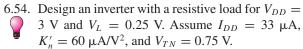

Design a resistively loaded NMOS inverter to operate from a 3.3-V power supply.

**PROBLEM** Design an inverter with a resistive load for  $V_{DD} = 3.3$  V and P = 0.1 mW with  $V_L = 0.2$  V. Assume  $K'_n = 60 \,\mu\text{A/V}^2$  and  $V_{TN} = 0.75$  V.

**SOLUTION** Known Information and Given Data: Circuit topology in Fig. 6.15;  $V_{DD}=3.3 \text{ V}, P=0.1 \text{ mW}, V_L=0.2 \text{ V}, K_n'=60 \text{ }\mu\text{A}/\text{V}^2, \text{ and } V_{TN}=0.75 \text{ V}$

**Unknowns:** Value of load resistor R; W/L ratio of switching transistor  $M_S$

**Approach:** Use the power dissipation specification to find the current  $I_{DD}$  for  $v_O = V_L$ . Use  $V_{DD}$ ,  $V_L$ , and  $I_{DD}$  to calculate R. Determine  $V_H$ . Use  $V_H$ ,  $V_L$ , and  $I_{DD}$  to find  $(W/L)_S$ .

**Assumptions:**  $M_S$  is off for  $v_I = V_L$ ;  $M_S$  is in the triode region for  $v_O = V_L$ .

**Analysis:** Using the power specification with the inverter circuit in Fig. 6.15, we have

$$I_{DD} = \frac{P}{V_{DD}} = \frac{10^{-4} \text{ W}}{3.3 \text{ V}} = 30.3 \text{ } \mu\text{A}$$

$$R = \frac{V_{DD} - V_L}{I_{DD}} = \frac{3.3 - 0.2}{30.3} \frac{\text{V}}{\mu\text{A}} = 102 \text{ } \text{k}\Omega$$

For  $v_I = V_L = 0.2$  V, the MOSFET will be off since 0.2 V is less than the threshold voltage, and the output high level will be  $V_H = V_{DD} = 3.3$  V. The triode region expression for the MOSFET drain current with  $v_{GS} = v_I = V_H$  and  $v_{DS} = v_O = V_L$  is

$$I_D = K'_n \left(\frac{W}{L}\right)_S \left(V_H - V_{TN} - \frac{V_L}{2}\right) V_L$$

Equating this expression to the drain current yields

30.3

$$\mu$$

A =  $(60 \times 10^{-6}) \left(\frac{W}{L}\right)_s \left(3.3 - 0.75 - \frac{0.2}{2}\right) 0.2 \rightarrow \left(\frac{W}{L}\right)_s = \frac{1.03}{1}$

Thus our completed design values are  $R = 102 \text{ k}\Omega$  and  $(W/L)_S = 1.03/1$ .

**Check of Results:** We should check the triode region assumption for the MOSFET for  $v_O = V_L$ :  $V_{GS} - V_{TN} = 3.3 - 0.75 = 2.55$  V, which is indeed greater than  $V_{DS} = 0.2$  V. Let us also double check the value of W/L by using it to calculate the drain current:

$$I_D = (60 \times 10^{-6}) \left(\frac{1.03}{1}\right) \left(3.3 - 0.75 - \frac{0.2}{2}\right) 0.2 = 30.3 \,\mu\text{A}$$

**Discussion:** This new design for a reduced voltage and reduced power requires a larger value of load resistor to limit the current, but a smaller device to conduct the reduced level of current.

Computer-Aided Analysis: Let us verify our design values with SPICE. The circuit drawn with a schematic capture tool is given below. The NMOS transistor uses the LEVEL = 1 model with KP = 6.0E-5, VTO = 1, W = 1.03U, and L = 1U. The Q-point of the transistor is  $(30.4 \, \mu A, 0.201 \, V)$ , which agrees with the design specifications.

**EXERCISE:** (a) Redesign the inverter in Ex. 6.2 to have  $V_L = 0.1 \text{ V}$  with  $R = 102 \text{ k}\Omega$ . (b) Verify your design with SPICE.

**ANSWER:**  $(W/L)_S = 2.09/1$

### 6.6.5 On-Resistance of the Switching Device

When the logic gate output is in the low state, the output voltage can also be calculated from a resistive voltage divider formed by the load resistor R and the **on-resistance**  $R_{\rm on}$  of the MOSFET, as in Fig. 6.18.

$$V_L = V_{DD} \frac{R_{\text{on}}}{R_{\text{on}} + R} = V_{DD} \frac{1}{1 + \frac{R}{R_{\text{on}}}}$$

(6.12)

where

$$R_{\rm on} = \frac{v_{DS}}{i_D} = \frac{1}{K_n' \frac{W}{L} \left( v_{GS} - V_{TN} - \frac{v_{DS}}{2} \right)}$$

(6.13)

Figure 6.18 Simplified representation of an inverter: (a) the off or nonconducting state, (b) the on or conducting state.

$R_{\rm on}$  must be much smaller than R in order for  $V_L$  to be small. It is important to recognize that  $R_{\rm on}$  represents a nonlinear resistor because the value of  $R_{\rm on}$  is dependent on  $v_{DS}$ , the voltage across the resistor terminals. All the NMOS gates that we study in this chapter demonstrate "ratioed" logic — that is, designs in which the on-resistance of the switching transistor must be much smaller than that of the load resistor in order to achieve a small value of  $V_L$  ( $R_{\rm on} \ll R$ ).

### **EXAMPLE 6.3** ON-RESISTANCE CALCULATION

Find the on-resistance for the MOSFET in the completed inverter design in Fig. 6.16(b).

**PROBLEM** What is the value of the on-resistance for the NMOS FET in Fig. 6.16 when the output voltage is at  $V_L$ ?

**SOLUTION** Known Information and Given Data:  $K_n' = 25 \,\mu\text{A/V}^2$ ,  $V_{TN} = 1 \,\text{V}$ , W/L = 2.06/1,  $V_{DS} = V_L = 0.25 \,\text{V}$

Unknowns: On-resistance of the switching transistor

**Approach:** Use the known values to evaluate Eq. (6.13).

**Assumptions:** The transistor is in the triode region of operation.

**Analysis:**  $R_{\rm on}$  can be found using Eq. (6.13).

$$R_{\rm on} = \frac{1}{\left(25 \times 10^{-6} \frac{A}{V^2}\right) \left(\frac{2.06}{1}\right) \left(5 - 1 - \frac{0.25}{2}\right) \text{ V}} = 5.0 \text{ k}\Omega$$

**Check of Results:** We can check this value by using it to calculate  $V_L$ :

$$V_L = V_{DD} \frac{R_{\text{on}}}{R_{\text{on}} + R} = 5 \text{ V} \frac{5 \text{ k}\Omega}{5 \text{ k}\Omega + 95 \text{ k}\Omega} = 0.25 \text{ V}$$

$R_{\rm on}=5~{\rm k}\Omega$  does indeed give the correct value of  $V_L$ . Note that  $R_{\rm on}\ll R$ . Checking the triode region assumption:  $V_{GS}-V_{TN}=5-1=4~{\rm V}$  and  $V_{DS}=V_L=0.25~{\rm V}$ .

**EXERCISE:** What value of  $R_{on}$  is indeed to set  $V_L = 0.20$  V? What is the new value of W/L

needed for the MOSFET to achieve this value of  $R_{on}$ ?

**Answers:** 3.96 k $\Omega$ ; 2.59/1

**EXERCISE:** What is the value of  $R_{on}$  for the MOSFET in Ex. 6.2? Use  $R_{on}$  to find  $V_L$ .

**ANSWERS:** 6.61 k $\Omega$ ; 0.201 V

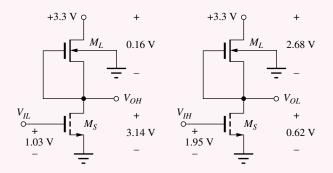

### 6.6.6 Noise Margin Analysis

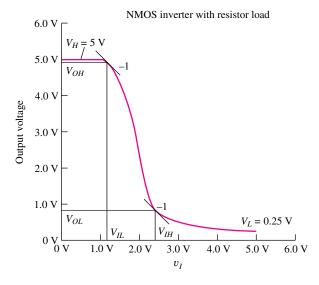

Figure 6.19 is a SPICE simulation of the voltage transfer function for the completed inverter design from Fig. 6.16. Now we are in a position to find the values of  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  that correspond to the points at which the slope of the voltage transfer characteristic for the inverter is equal to -1, as defined in Sec. 6.2. Our analysis begins with the expression for the load line, repeated here from Eq. (6.8):

$$v_O = V_{DD} - i_D R \tag{6.14}$$

Figure 6.19 Simulated voltage transfer characteristic of an NMOS logic gate with resistive load.

### **6.6.7** CALCULATION OF $V_{IL}$ AND $V_{OH}$

Referring back to Fig. 6.15 with  $v_I = V_{IL}$ ,  $v_{GS}$  (=  $v_I$ ) is small and  $v_{DS}$  (=  $v_O$ ) is large, so we expect the MOSFET to be operating in saturation, with drain current given by

$$i_D = (K_n/2)(v_{GS} - V_{TN})^2$$

where  $K_n = K'_n(W/L)$  and  $v_{GS} = v_I$

Substituting this expression for  $i_D$  in load-line Eq. (6.14),

$$v_O = V_{DD} - \frac{K_n}{2} (v_I - V_{TN})^2 R \tag{6.15}$$

and taking the derivative of  $v_O$  with respect to  $v_I$  results in

$$\frac{dv_O}{dv_I} = -K_n(v_I - V_{TN})R \tag{6.16}$$

Setting this derivative equal to -1 for  $v_I = V_{IL}$  yields

$$V_{IL} = V_{TN} + \frac{1}{K_n R}$$

with  $V_{OH} = V_{DD} - \frac{1}{2K_n R}$  (6.17)

We see that the value of  $V_{IL}$  is slightly greater than  $V_{TN}$ , since the input must exceed  $V_{TN}$  for  $M_S$  to begin conduction, and  $V_{OH}$  is slightly less than  $V_{DD}$ . The  $1/K_nR$  terms represent the ratio of the transistor's transconductance parameter to the value of the load resistor. As  $K_n$  increases for a given value of R,  $V_{IL}$  decreases and  $V_{OH}$  increases.

**EXERCISE:** Show that  $(1/K_nR)$  has the units of voltage.

### 6.6.8 CALCULATION OF $V_{IH}$ AND $V_{OL}$

For  $v_I = V_{IH}$ ,  $v_{GS}$  is large and  $v_{DS}$  is small, so we now expect the MOSFET to be operating in the triode region with drain current given by  $i_D = K_n[v_{GS} - V_{TN} - (v_{DS}/2)]v_{DS}$ . Substituting this expression for  $i_D$  into Eq. (6.14) and realizing that  $v_O = v_{DS}$  yields

$$v_O = V_{DD} - K_n R \left( v_I - V_{TN} - \frac{v_O}{2} \right) v_O$$

or

$$\frac{v_O^2}{2} - v_O \left[ v_I - V_{TN} + \frac{1}{K_n R} \right] + \frac{V_{DD}}{K_n R} = 0$$

(6.18)

Solving for  $v_O$  and then setting  $dv_O/dv_I = -1$  for  $v_I = V_{IH}$  yields

$$V_{IH} = V_{TN} - \frac{1}{K_n R} + 1.63 \sqrt{\frac{V_{DD}}{K_n R}}$$

with  $V_{OL} = \sqrt{\frac{2V_{DD}}{3K_n R}}$  (6.19)

In this case, we find that the values of  $V_{OL}$  and  $V_{IH}$  depend on the ratio  $V_{DD}/K_nR$ .

### **EXAMPLE 6.4** NOISE MARGIN CALCULATION FOR THE RESISTIVE LOAD INVERTER

Find the noise margins associated with the inverter design in Fig. 6.16(b).

**PROBLEM** Calculate the noise margins for the inverter in Fig. 6.16(b).

**SOLUTION** Known Information and Given Data: The NMOS inverter circuit with resistor load in Fig. 6.15 with  $R = 95 \text{ k}\Omega$ ,  $(W/L)_S = 2.06/1$ ,  $K'_n = 25 \text{ }\mu\text{A/V}^2$ , and  $V_{TN} = 1 \text{ V}$

**Unknowns:** The values of  $V_{IL}$ ,  $V_{OH}$ ,  $V_{IH}$ ,  $V_{OL}$ ,  $NM_L$ , and  $NM_H$

**Approach:** Use the given data to evaluate Eqs. (6.17) and (6.18). Use the results to find the noise margins:  $NM_H = V_{OH} - V_{IH}$  and  $NM_L = V_{IL} - V_{OL}$ .

**Assumptions:** Equation (6.17) assumes saturation region operation; Eq. (6.18) assumes triode region operation.

Analysis: For the inverter design in Fig. 6.16(b),

$$V_{TN} = 1 \text{ V}$$

$K'_n \frac{W}{I} = 25 \frac{2.06}{1} \frac{\mu A}{V^2} = 51.5 \frac{\mu A}{V^2}$   $R = 95 \text{ k}\Omega$

Evaluating Eq. (6.17),

$$V_{IL} = 1 + \frac{1}{(51.5 \,\mu\text{A})(95 \,\text{k}\Omega)} = 1.20 \,\text{V}$$

and  $V_{OH} = 5 - \frac{1}{2(51.5 \,\mu\text{A})(95 \,\text{k}\Omega)} = 4.90 \,\text{V}$

and Eq. (6.18),

$$V_{IH} = 1 - \frac{1}{(51.5 \,\mu\text{A})(95 \,\text{k}\Omega)} + 1.63\sqrt{\frac{5}{(51.5 \,\mu\text{A})(95 \,\text{k}\Omega)}} = 2.44 \,\text{V}$$

$$V_{OL} = \sqrt{\frac{2(5)}{3(51.5 \,\mu\text{A})(95 \,\text{k}\Omega)}} = 0.83 \,\text{V}$$

The noise margins are found to be

$$NM_H = 4.90 - 2.44 = 2.46 \text{ V}$$

and  $NM_L = 1.20 - 0.83 = 0.37 \text{ V}$

**Check of Results:** The values of  $V_{IL}$ ,  $V_{OH}$ ,  $V_{IH}$ , and  $V_{OL}$  all agree well with the simulation results in Fig. 6.19. Equation (6.17) is based on the assumption of saturation region operation. We should check to see if this assumption is consistent with the results in Eq. (6.17):  $v_{DS} = 4.90$  and  $v_{GS} - V_{TN} = 1.2 - 1.0 = 0.2$ . Because  $v_{DS} > (v_{GS} - V_{TN})$ , our assumption was correct. Similarly, Eq. (6.18) is based on the assumption of triode region operation. Checking this assumption, we have  $v_{DS} = 0.83$  and  $v_{GS} - V_{TN} = 2.44 - 1.0 = 1.4$ . Since  $v_{DS} < (v_{GS} - V_{TN})$ , our assumption was correct.

**Discussion:** Our analysis indicates that a long chain of inverters can tolerate electrical noise and process variations equivalent to 0.37 V in the low-input state and more than 2.4 V in the high state. Note that it is common for the values of the two noise margins to be substantially different, as illustrated here.

EXERCISE: (a) Find the noise margins for the inverter in Ex. 6.2. (b) Verify your results with SPICE.

**ANSWERS:**  $NM_L = 0.32 \text{ V}; NM_H = 1.45 \text{ V} (V_{IL} = 0.090 \text{ V}, V_{OH} = 3.22 \text{ V}, V_{IH} = 1.77 \text{ V}, V_{OL} = 0.591 \text{ V})$

As mentioned earlier,  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$ , as specified by a manufacturer, actually represent guaranteed specifications for a given logic family and take into account the full range of variations in technology parameters, temperature, power supply, loading conditions, and so on. In Ex. 6.4, we have computed only  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  and the noise margins under nominal conditions at room temperature.

### **6.6.9 LOAD RESISTOR PROBLEMS**

The NMOS inverter with resistive load has been used to introduce the concepts associated with static logic gate design. Although a simple discrete component logic gate could be built using this circuit, IC realizations do not use resistive loads because the resistor would take up far too much area.

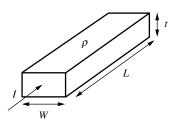

To explore the load resistor problem further, consider the rectangular block of semiconductor material in Fig. 6.20 with a resistance given by

$$R = \frac{\rho L}{tW} \tag{6.20}$$

where  $\rho = \text{resistivity}$

L, W, t = length, width, thickness of resistor, respectively

**Figure 6.20** Geometry for a simple rectangular resistor.

In an integrated circuit, a resistor might typically be fabricated with a thickness of 1  $\mu$ m in a silicon region with a resistivity of 0.001  $\Omega \cdot$  cm. For these parameters, the 95-k $\Omega$  load resistor in the previous section would require the ratio of L/W to be

$$\frac{L}{W} = \frac{Rt}{\rho} = \frac{(9.5 \times 10^4 \ \Omega)(1 \times 10^{-4} \ \text{cm})}{0.001 \ \Omega \cdot \text{cm}} = \frac{9500}{1}$$

If the resistor width W were made a minimum line width of 1  $\mu$ m, which we will call the **minimum** feature size F, then the length L would be 9500  $\mu$ m, and the area would be 9500  $\mu$ m<sup>2</sup>.

For the switching device  $M_S$ , W/L was found to be 2.06/1. If the device channel length is made equal to the minimum feature size of 1  $\mu$ m, then the gate area of the NMOS device is only 2.06  $\mu$ m<sup>2</sup>. Thus, the load resistor would consume more than 4000 times the area of the switching transistor  $M_S$ . This is simply not an acceptable utilization of area in IC design. The solution to this problem is to replace the load resistor with a transistor.

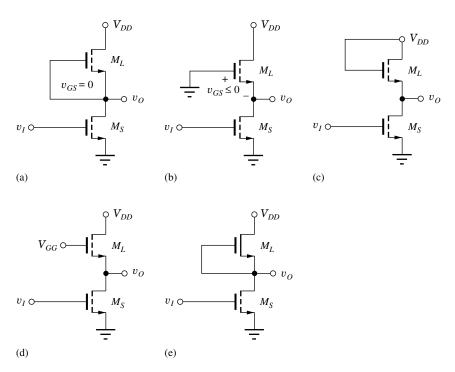

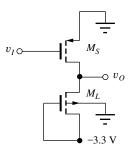

### 6.6.10 Transistor Alternatives to the Load Resistor

The two-terminal resistor is replaced with a three-terminal MOSFET, and four possibilities are shown in Fig. 6.21. One possibility is to connect the gate to the source, as in Fig. 6.21(a). However, for this case  $v_{GS} = 0$ , and MOSFET  $M_L$  will be nonconducting, assuming it is an enhancement-mode device with  $V_{TN} > 0$ . A similar problem exists if the gate is grounded, as in Fig. 6.21(b).

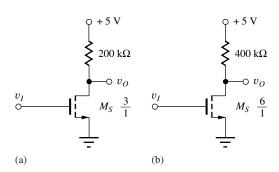

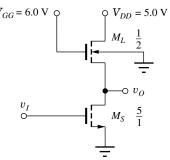

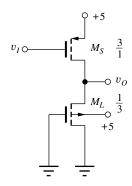

**Figure 6.21** NMOS inverter load device options: (a) NMOS inverter with gate of the load device connected to its source, (b) NMOS inverter with gate of the load device grounded, (c) saturated load inverter, (d) linear load inverter, and (e) Depletion load inverter. Note that (a) and (b) are not useful.

Here again, the connection forces  $v_{GS} \leq 0$ , and the load device is turned off. Neither of these two connections work because an enhancement-mode load device can never conduct current under these conditions.

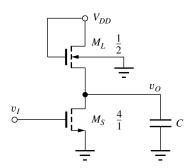

A workable choice is to connect the gate to the drain, as in Fig. 6.21(c). Here  $v_{DS} = v_{GS}$ , and the load device will operate in the saturation region because  $v_{GS} - V_{TN} = v_{DS} - V_{TN} \le v_{DS}$  for  $V_{TN} \ge 0$ . Because the connection forces the **load transistor** to always operate in the saturation region, we refer to this inverter as the **saturated load inverter**. Another solution, called the **linear load inverter**, is shown in Fig. 6.21(d). In this circuit, the gate of the load device is biased by a second voltage that maintains  $M_L$  in the triode (linear) region.

The circuit configuration in Fig. 6.21(a) can be made to work if load transistor  $M_L$  is converted to a depletion-mode device (i.e.,  $V_{TN} < 0$ ), as redrawn in Fig. 6.21(e). This form of NMOS logic provides that highest performance at the cost of additional fabrication process, because the threshold of  $M_L$  must be modified to convert it from an enhancement-mode transistor to a depletion-mode device.

Saturated load logic played an important role in the history of electronic circuits. This form of logic was used in the design of the early microprocessors, first in PMOS and later in NMOS technology, and this logic family provides a basic foundation for understanding many of the issues related to MOS VLSI design. Thus, we explore its design in Sec. 6.7.

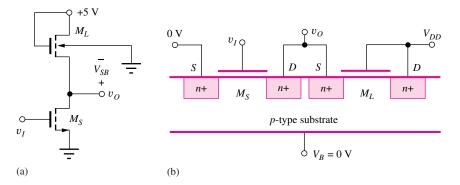

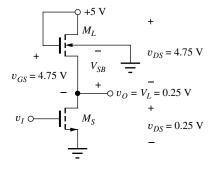

# 6.7 STATIC DESIGN OF THE NMOS SATURATED LOAD INVERTER

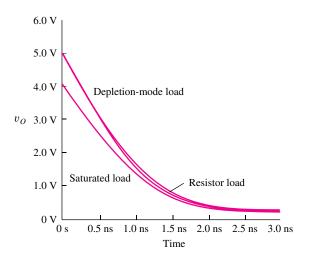

Figure 6.22(a) shows the circuit diagram for the saturated load inverter, and Fig. 6.22(b) shows the cross section of the inverter in integrated circuit form. Here we see a very important aspect of the structure. The substrate is common to both transistors; thus, the substrate voltage must be the

**Figure 6.22** (a) Saturated load inverter. (b) Cross section of two integrated MOSFETs forming an inverter.

same for both  $M_S$  and  $M_L$  in the inverter, and the substrate terminal of  $M_L$  cannot be connected to its source as originally indicated in Fig. 6.21(c). This extra substrate terminal is most commonly connected to ground (0 V) (although voltages of -5 V and -8 V have been used in the past). For a substrate voltage of 0 V,  $v_{SB}$  for the switching device is always zero, but  $v_{SB}$  for the load device  $M_L$  changes as  $v_O$  changes. In fact,  $v_{SB} = v_O$ , as indicated in Fig. 6.22(a). The threshold voltages of transistors  $M_S$  and  $M_L$  will no longer be the same, and we will indicate the different values by  $V_{TNS}$  and  $V_{TNL}$ , respectively.

For the design of the saturated load inverter, we use the same circuit conditions that were used for the case of the resistive load ( $I_{DD} = 50 \,\mu\text{A}$  with  $V_{DD} = 5 \,\text{V}$  and  $V_L = 0.25 \,\text{V}$ ). We first choose the W/L ratio of  $M_L$  to limit the operating current and power in the inverter. Because  $M_L$  is forced to operate in saturation by the circuit connection, its drain current is given by

$$i_D = \frac{K'_n}{2} \left(\frac{W}{L}\right)_L (v_{GS} - V_{TNL})^2$$

(6.21)

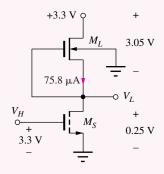

For the circuit conditions in Fig. 6.23, load device  $M_L$  has  $v_{GS} = 4.75$  V when  $v_O = 0.25$  V.

Before we can calculate W/L, we must find the value of threshold voltage  $V_{TNL}$ , which is determined by the body effect relation represented by Eq. (4.26) in Chapter 4:

$$V_{TN} = V_{TO} + \gamma \left( \sqrt{v_{SB} + 2\phi_F} - \sqrt{2\phi_F} \right) \tag{6.22}$$

Figure 6.23 Saturated load inverter with  $v_O = V_L$ .

| TABLE 6.8          |                                                                   |                                          |  |

|--------------------|-------------------------------------------------------------------|------------------------------------------|--|

|                    | NMOS ENHANCEMENT-MODE<br>DEVICE PARAMETERS                        | NMOS DEPLETION-MODE<br>DEVICE PARAMETERS |  |

| $V_{TO}$           | $\begin{array}{c} 1 \text{ V} \\ 0.5 \sqrt{\text{V}} \end{array}$ | $-3 \text{ V}$ $0.5 \sqrt{\text{V}}$     |  |

| $\gamma \ 2\phi_F$ | 0.5 V<br>0.6 V                                                    | 0.5 V<br>0.6 V                           |  |

| $K'_n$             | $25 \mu A/V^2$                                                    | $25 \mu A/V^2$                           |  |

where  $V_{TO}$  = zero bias value of  $V_{TN}$  (V)

$\gamma = \text{body effect parameter } (\sqrt{V})$

$2\phi_F = \text{surface potential parameter (V)}$

For the rest of the discussion in this chapter, we use the set of device parameters given in Table 6.8. For the load transistor, we have

$$v_{SR} = v_S - v_R = 0.25 \text{ V} - 0 \text{ V} = 0.25 \text{ V}$$

and

$$V_{TNL} = 1 + 0.5(\sqrt{0.25 + 0.6} - \sqrt{0.6}) = 1.07 \text{ V}$$

Now, we can find the W/L ratio for the load transistor:

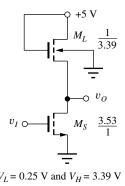

$$\left(\frac{W}{L}\right)_{L} = \frac{2i_{D}}{K'_{n}(v_{GS} - V_{TN})^{2}} = \frac{2 \cdot 50 \,\mu\text{A}}{25\frac{\mu\text{A}}{V^{2}}(4.75 - 1.07)^{2}} = \frac{1}{3.39}$$

(6.23)

Note that the length of this load device is larger than its width. In most digital IC designs, one of the two dimensions will be made as small as possible corresponding to the minimum feature size in one direction. The W/L ratio is usually written with the smallest number normalized to unity. For  $F = 1 \mu m$ , the gate area of  $M_L$  is now only 3.52  $\mu m^2$ , which is comparable to the area of  $M_S$ .

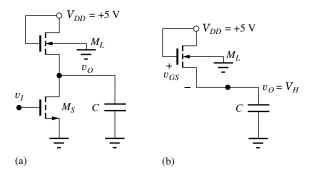

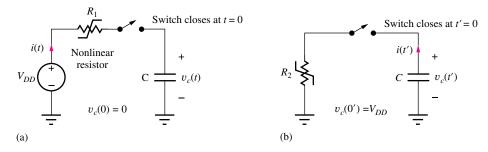

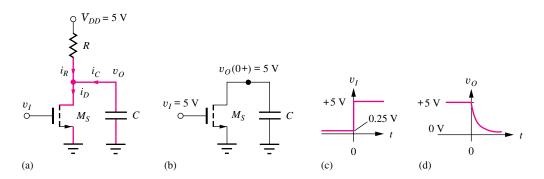

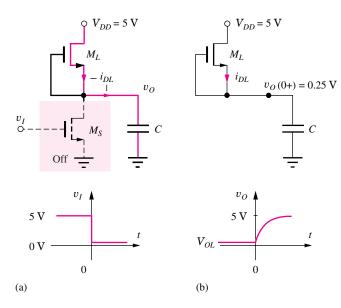

### **6.7.1** CALCULATION OF $V_H$

Unfortunately, the use of the saturated load device has a detrimental effect on other characteristics of the logic gate. The value of  $V_H$  will no longer be equal to  $V_{DD}$ . In order to understand this effect, it is helpful to imagine a capacitive load attached to the logic gate, as in Fig. 6.24. Consider the logic gate with  $v_I = V_L$  so that  $M_S$  is turned off. When  $M_S$  turns off, load device  $M_L$  charges capacitor C until the current through  $M_L$  becomes zero, which occurs when  $v_{GS} = V_{TN}$ :

$$v_{GS} = V_{DD} - V_H = V_{TN}$$

or  $V_H = V_{DD} - V_{TN}$  (6.24)

Thus, for the NMOS inverter using a saturated load, the output voltage reaches a maximum value equal to one threshold voltage drop below the power supply voltage  $V_{DD}$ . Without body effect, the output would reach  $V_H = 5 - 1 = 4$  V. Compared to the original inverter with a resistive load, the high output level is degraded from 5 V to 4 V.

Figure 6.24 (a) Inverter with load capacitance. (b) High output level is reached when  $v_I = V_L$  and  $M_S$  is off.

Body effect makes the situation even worse. As the output voltage increases toward  $V_H$ ,  $v_{SB}$  increases, the threshold voltage increases above  $V_{TO}$  (see Eq. 6.22), and the steady-state value of  $V_H$  is less than 4 V. When  $v_O$  reaches  $V_H$ , this relationship must be true because  $v_{SB} = V_H$ :

$$V_{H} = V_{DD} - V_{TNL} = V_{DD} - \left[ V_{TO} + \gamma \left( \sqrt{V_{H} + 2\phi_{F}} - \sqrt{2\phi_{F}} \right) \right]$$

(6.25)

$V_H$  is found using this quadratic formula

$$V_{H} = \frac{B - \sqrt{B^{2} - 4C}}{2} \quad \text{with}$$

$$B = 2\left[V_{DD} - V_{TO} + \gamma\sqrt{2\phi_{F}} + \frac{\gamma^{2}}{2}\right] \quad \text{and} \quad C = (V_{DD} - V_{TO})^{2} + 2\gamma\sqrt{2\phi_{F}}(V_{DD} - V_{TO})$$

Using Eq. (6.25) with the parameters from Table 6.8 and  $V_{DD} = 5$  V, we can solve for  $V_H$ , which yields the following quadratic equation:

$$(V_H - 4 - 0.5\sqrt{0.6})^2 = 0.25(V_H + 0.6)$$

Solving for  $V_H$  gives

$$V_H = 3.39 \,\text{V}, \, \frac{5.64}{5.64} \,\text{V}$$

In this circuit, the steady-state value of  $V_H$  cannot exceed the power supply voltage  $V_{DD}$  (actually it cannot exceed  $V_{DD} - V_{TNL}$ ), so the answer must be  $V_H = 3.39$  V. We can check our result for  $V_{OH}$  by computing the threshold voltage of the load device using Eq. (6.22):

$$V_{TNL} = 1 \text{ V} + 0.5 \sqrt{\text{V}} \left( \sqrt{(3.39 + 0.6) \text{ V}} - \sqrt{0.6 \text{ V}} \right) = 1.61 \text{ V}$$

and

$$V_H = V_{DD} - V_{TNL} = 5 - 1.61 = 3.39 \text{ V}$$

which checks with the previous calculation of  $V_H$ .

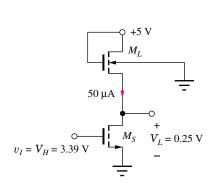

### **6.7.2** CALCULATION OF $(W/L)_S$

Now we are in a position to complete the inverter design by calculating W/L for the switching transistor. The bias conditions for  $v_O = V_L$  appear in Fig. 6.25 in which the drain current of  $M_S$  must equal the design value of 50  $\mu$ A. For  $V_{GS} = 3.39$  V,  $V_{DS} = 0.25$  V, and  $V_{TNS} = 1$  V, the

Figure 6.25 Bias conditions used to determine  $(W/L)_S$ .

Figure 6.26 Inverter design with saturated load devices.

switching transistor is operating in the triode region. Therefore,

$$i_{D} = K'_{n} \left(\frac{W}{L}\right)_{S} \left(v_{GS} - V_{TNS} - \frac{v_{DS}}{2}\right) v_{DS}$$

$$50 \,\mu\text{A} = 25 \frac{\mu\text{A}}{\text{V}^{2}} \left(\frac{W}{L}\right)_{S} \left(3.39 - 1 - \frac{0.25}{2}\right) 0.25 \,\text{V}^{2}$$

$$\left(\frac{W}{L}\right)_{S} = \frac{3.53}{1}$$

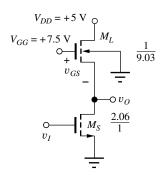

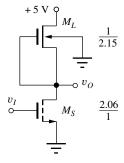

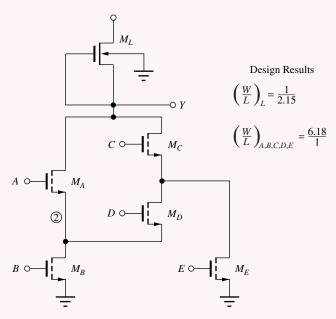

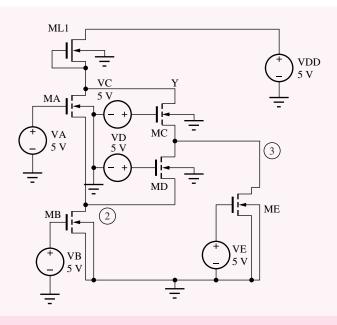

The final inverter design appears in Fig. 6.26 in which  $(W/L)_S = 3.53/1$  and  $(W/L)_L = 1/3.39$ . The size of the switching device has been increased over that of the resistive load case to compensate for the reduced logic high level of 3.39 V.

**EXERCISE:** Find  $V_H$  for the inverter in Fig. 6.22(a) if  $V_{TO} = 0.75$  V. Assume the other parameters remain constant.

ANSWER: 3.60 V

**EXERCISE:** (a) What value of  $(W/L)_S$  is required to achieve  $V_L = 0.15$  V in Fig. 6.25? Assume that  $i_D = 50$   $\mu$ A. What is the new value of  $V_{TNL}$  for  $V_O = V_L$ ? What value of  $(W/L)_L$  is required to set  $i_D = 50$   $\mu$ A for  $V_L = 0.15$  V? (b) Repeat for  $V_L = 0.10$  V.

Answer: (a) 5.76/1, 1.05 V, 1/3.61; (b) 8.55/1, 1.03 V, 1/3.74

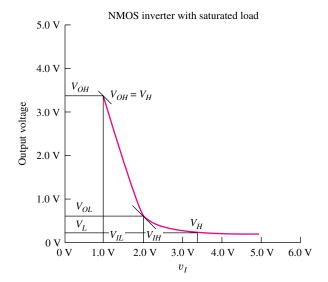

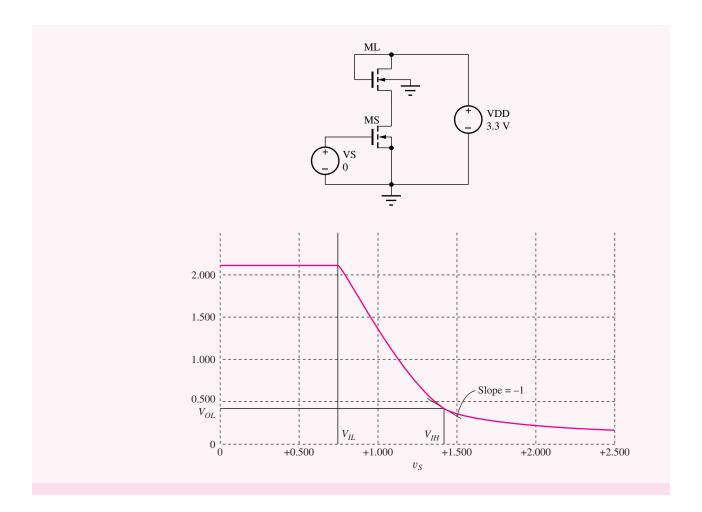

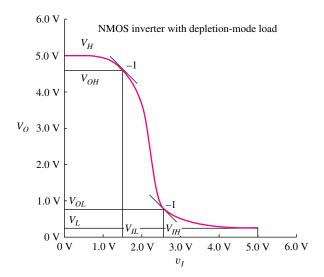

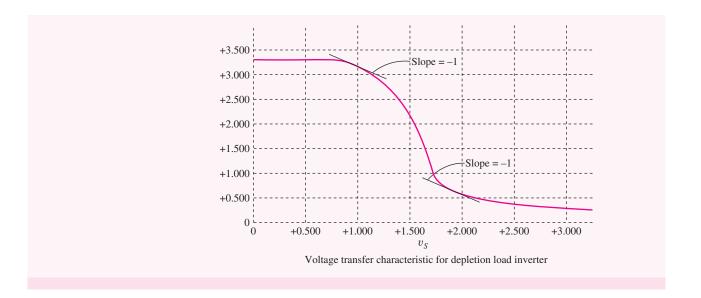

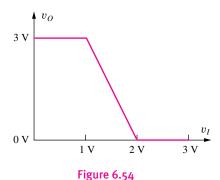

Figure 6.27 shows the results of SPICE simulation of the voltage transfer function for the final design in Fig. 6.26. For low values of input voltage, the output is constant at 3.4 V. As the input voltage increases, the slope of the transfer function abruptly changes at the point at which the switching transistor begins to conduct, as the input voltage exceeds the threshold voltage of  $M_S$ . As the input voltage continues to increase, the output voltage decreases rapidly and ultimately reaches the design value of 0.25 V for an input of 3.4 V.

Figure 6.27 SPICE simulation of the voltage transfer function for the NMOS inverter with saturated load.

### STATIC LOGIC INVERTER DESIGN STRATEGY

- 1. Given design values of  $V_{DD}$ ,  $V_L$ , and the power level, find  $I_{DD}$  from  $V_{DD}$  and power.

- 2. Assume switching transistor  $M_S$  is off, and find the high output voltage level  $V_H$ .

- 3. Apply  $V_H$  to the inverter input and calculate  $(W/L)_S$  of the switching transistor based upon design values of  $V_L$  and  $I_{DD}$ .

- 4. Calculate load resistor value or  $(W/L)_L$  for the load transistor based on design values of  $V_L$  and  $I_{DD}$ .

- 5. Check operating region assumptions for  $M_S$  and  $M_L$  for  $v_O = V_L$ .

- 6. Check overall design with SPICE simulation.

# **DESIGN EXAMPLE 6.5**

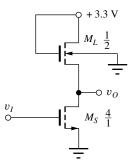

#### DESIGN OF AN INVERTER EMPLOYING A SATURATED LOAD DEVICE

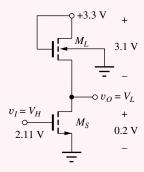

Now let's design a saturated load inverter to operate from a 3.3-V supply including the influence of body effect on the transistor design.

PROBLEM Design a saturated load inverter similar to that of Fig. 6.26 with  $V_{DD}=3.3$  V and  $V_L=0.2$  V. Assume  $I_{DD}=30$   $\mu$ A,  $K'_n=25$   $\mu$ A/V<sup>2</sup>,  $V_{TN}=0.75$  V,  $\gamma=0.5$   $\sqrt{V}$ , and  $2\phi_F=0.6$  V.

**SOLUTION** Known Information and Given Data: Circuit topology in Fig. 6.26;  $V_{DD} = 3.3 \text{ V}$ ,  $I_{DD} = 30 \text{ }\mu\text{A}$ ,  $V_L = 0.2 \text{ V}$ ,  $K'_n = 25 \text{ }\mu\text{A}/\text{V}^2$ ,  $V_{TO} = 0.75 \text{ V}$ ,  $\gamma = 0.5 \sqrt{\text{V}}$ , and  $2\phi_F = 0.6 \text{ V}$

**Unknowns:** W/L ratios of the load and switching transistors  $M_S$  and  $M_L$

**Approach:** First determine  $V_H$  including the influence of body effect on the load transistor threshold voltage by evaluating Eq. (6.25). Use  $V_H$ , and the specified values of  $V_L$  and  $I_D$  to find  $(W/L)_S$ . Use  $I_D$  and the voltages in the circuit to find  $(W/L)_L$ .

**Assumptions:**  $M_S$  is off for  $v_I = V_L$ . For  $v_O = V_L$ ,  $M_S$  is in the triode region, and  $M_L$  is in the saturation region.

**Analysis:** For the values associated with this technology, Eq. (6.25) becomes

$$V_H = 3.3 - \left[0.75 + 0.5\left(\sqrt{V_H + 0.6} - \sqrt{0.6}\right)\right]$$

and rearranging this equation gives

$$V_H^2 - 6.125V_H + 8.476 = 0$$

for which  $V_H = 2.11 \text{ V}, \frac{4.01 \text{ V}}{4.01 \text{ V}}$

Since,  $V_H$  cannot exceed  $V_{DD}$ , the correct choice must be  $V_H = 2.11$  V. Note that an extra digit was included in the calculation to increase the precision of the result.

The transistor operating conditions for the load and switching transistors appear in the circuit below for  $v_O = V_L$ . The triode region expression for the switching transistor drain current with  $v_I = V_H$  and  $v_O = V_L$  is

$$I_{DS} = K'_n \left(\frac{W}{L}\right)_S \left(V_H - V_{TN} - \frac{V_L}{2}\right) V_L$$

Equating this expression to the drain current yields

30

$$\mu$$

A =  $(25 \times 10^{-6}) \left(\frac{W}{L}\right)_{S} \left(2.11 - 0.75 - \frac{0.2}{2}\right) 0.2 \rightarrow \left(\frac{W}{L}\right)_{S} = \frac{4.76}{1}$

To find the W/L ratio for the load device, the saturation region expression is evaluated at a drain current of 30  $\mu$ A. We must recalculate the threshold voltage since the body voltage of the load is 0.2 V when  $v_O = V_L = 0.2$  V.

$$I_{DL} = \frac{K'_n}{2} \left(\frac{W}{L}\right)_L (V_{GSL} - V_{TNL})^2$$

$$V_{TNL} = 0.75 + 0.5 \left(\sqrt{0.2 + 0.6} - \sqrt{0.6}\right) = 0.81 \text{ V}$$

$$30 \,\mu\text{A} = \frac{25 \frac{\mu\text{A}}{V^2}}{2} \left(\frac{W}{L}\right)_L (3.3 - 0.2 - 0.81)^2 \rightarrow \left(\frac{W}{L}\right)_L = \frac{1}{2.19}$$

Our completed design values are  $(W/L)_S = 4.76/1$  and  $(W/L)_L = 1/2.19$ .

**Check of Results:** We must check the triode and saturation region assumptions for the two MOSFETs: For the switch,  $V_{GS} - V_{TN} = 2.11 - 0.75 = 1.36$  V, which is greater than  $V_{DS} = 0.2$  V, and the triode region assumption is correct. For the load device,  $V_{GS} - V_{TN} = 3.1 - 0.81 = 2.29$  V and  $V_{DS} = 3.1$  V, which is consistent with the saturation region of

operation. We can double check our  $V_H$  calculation by using it to find the threshold of  $M_L$ :

$$V_{TNL} = 0.75 + 0.5(\sqrt{2.11 + 0.6} - \sqrt{0.6}) = 1.19 \text{ V}$$

This is correct since  $V_H + V_{TNL} = 2.11 + 1.19 = 3.3$  V, which must equal the value of  $V_{DD}$ . Let us also double check the values of W/L by using them to recalculate the drain currents:

$$I_D = (25 \times 10^{-6}) \left(\frac{4.76}{1}\right) \left(2.11 - 0.75 - \frac{0.2}{2}\right) 0.2 = 30.0 \,\mu\text{A} \quad \checkmark$$

$$I_{DL} = \frac{25 \frac{\mu\text{A}}{V^2}}{2} \left(\frac{1}{2.19}\right) (3.3 - 0.2 - 0.81)^2 = 29.9 \,\mu\text{A} \quad \checkmark$$

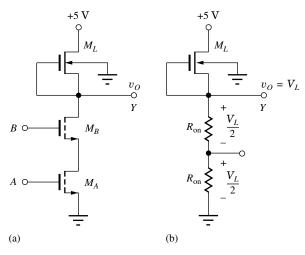

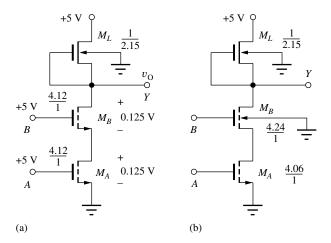

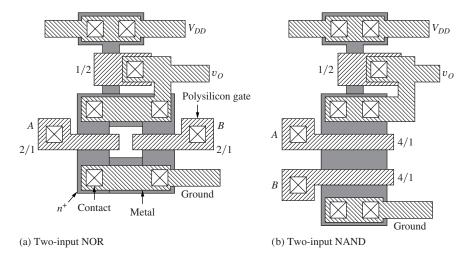

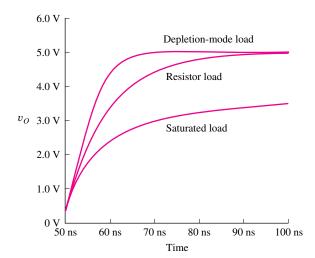

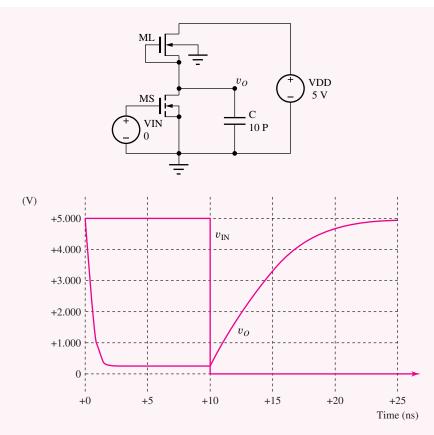

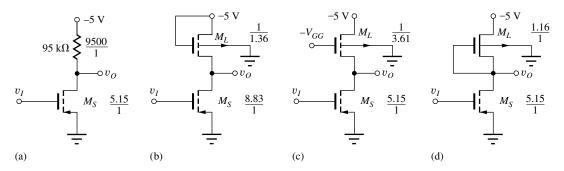

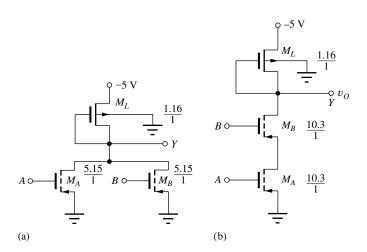

Both results agree within round off error.